# Memrisys 2024

# -Poster Session-

| Boyoung<br>Jeong  | Analog weight update by tunable interfacial energy barrier by Li ion redistribution<br>in Pt/p-LiCoOx/p-NiO/Pt memristor for neuromorphic computing |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Donghoon<br>Shin  | Heterogeneous Density-based Clustering with Dual-functional Memristive Array                                                                        |  |  |

| Guoyang<br>Huang  | Memimpedance-based Neural Adaptation Circuit with Hybrid CMOS/Volatile<br>Memristor LIF Neuron                                                      |  |  |

| Hina Kitano       | Reservoir computing using graphene-based solid state electric double layer transistors                                                              |  |  |

| Hongwoon<br>Yun   | Neuromorphic Computing based on Two-terminal Au nanoparticle Floating-gate<br>Memristor                                                             |  |  |

| Hongxiao<br>Duan  | 1T-1PD pixel with broadband and reconfigurable characteristics                                                                                      |  |  |

| Hyungsuk<br>Oh    | Silicon/Graphene Optical Sensors and Neuromorphic system for Visual Cell<br>Emulation                                                               |  |  |

| Jamie Steel       | Physical Reservoir Computing with Percolating Networks of Nanoparticles                                                                             |  |  |

| Jieun Kim         | Cluster type selector-less 1R memristor array for spiking neural network                                                                            |  |  |

| Jiyeon Ryu        | Energy efficient, high performance resistive memory device with Ag/VOx/Pt structure by facilitated Ag filament formation                            |  |  |

| Keunho Soh        | Stochastic Ion-motion Mediated Volatile Threshold Switching Memristor Enables<br>Probabilistic Computing                                            |  |  |

| László Pósa       | Size-Dependent Study on Nanosized VO2 Phase Change Memory Devices                                                                                   |  |  |

| Leon<br>Brackmann | Improved Stateful Logic Designs based on Memristive 1T-1R Arrays                                                                                    |  |  |

| Maki<br>Nishimura | Computational performance of Magnonic Reservoir Computing with Increased<br>Number of Detectors                                                     |  |  |

| Marina<br>Sparvoli        | Circuit emulating neuronal response based on Ga2O3 photomemristors                                                                                   |  |  |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Mihyang<br>Park           | Self-rectifying Two-terminal Vertical Floating Memristor                                                                                             |  |  |

| Minh Chien<br>Nguyen      | Reconfigurable Non-volatile Floating Gate Memory based on van der Waals<br>Heterostructure for Multi-functional Devices                              |  |  |

| Naoya<br>Yamashita        | Development and Resistive Switching Properties of Amorphous GaOx Four-<br>Terminal Crossbar Memristor                                                |  |  |

| Néstor<br>Ghenzi          | Reconfigurable Devices for Enhanced Reservoir Computing                                                                                              |  |  |

| Peter<br>Hayoung<br>Chung | Self-selective Crossbar Synapse Array with n-ZnO/p-NiOx/n-ZnO Structure for Neuromorphic Computing                                                   |  |  |

| Richard<br>Schroedter     | An ErMnO3 memristive spiking neuristor                                                                                                               |  |  |

| Rishona<br>Daniels        | V-VTEAM: A Compact Behavioral Model for Volatile Memristors                                                                                          |  |  |

| Rohit Attri               | Emergence of In Materia Intelligence in Energy-efficient Neuromorphic Devices realized using Self-forming Hierarchical Structures                    |  |  |

| Seokki Son                | Multi-level switching in 1T1R memristive cells: A simulation approach by compact model                                                               |  |  |

| Sola Moon                 | Reservoir Computing for Pattern Recognition using Gd-doped CeO2/CeO2 Bi-layer<br>Memristor                                                           |  |  |

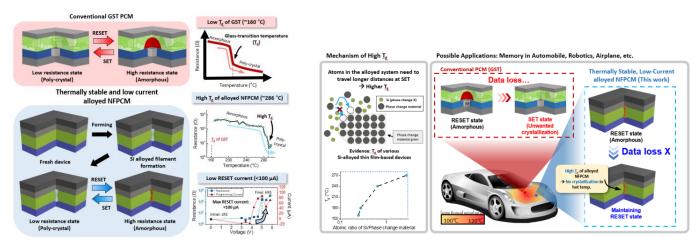

| Su-Jin Sung               | Low-Power and Thermally Stable Phase Change Memory by Material Engineering of Phase-Changeable Nano-Filament                                         |  |  |

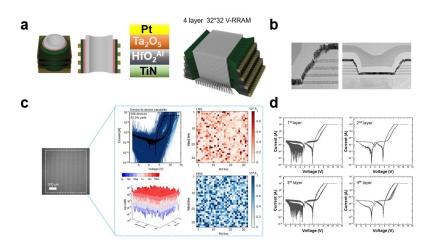

| Tae Won<br>Park           | Fabrication of 4k Density Vertical Resistive Switching Memory for Neuromorphic<br>Applications                                                       |  |  |

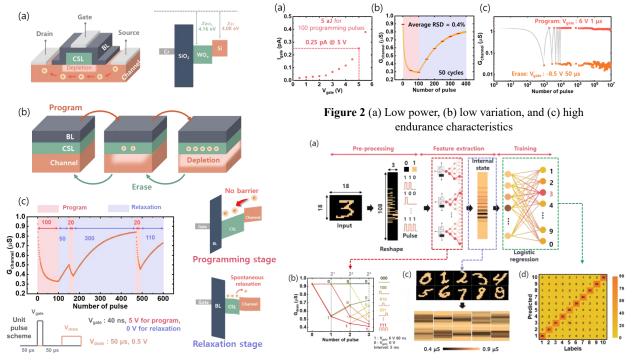

| Taehoon<br>Park           | Low Power and Reliable Dynamic Memtransistor with Step-Wise Potential Barrier<br>for Energy-Efficient Computing                                      |  |  |

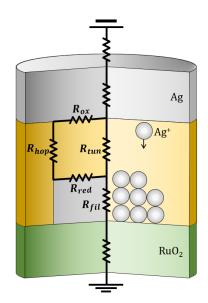

| Taeyoung<br>Jeong         | A combined approach of numerical simulation and ab initio calculations on Ag/HfO2/RuO2 diffusive memristor for probabilistic computation application |  |  |

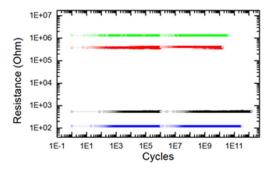

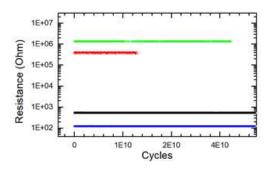

| Timo Oster                | Long-Term Stability Testing of Memristors: Pulsed Read Endurance Measurements<br>On Yttria-based OxRAM                                               |  |  |

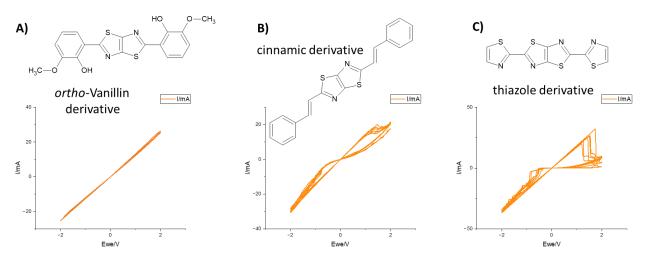

| Tomasz<br>Mazur  | Thiazolothiazole Derivatives for Information Processing with Fine-Tuning<br>Capabilities                                          |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|

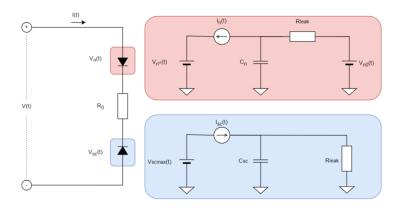

| Viet Cuong<br>Vu | Circuit-Based Modelling of Current Transients within the Memristive Devices<br>Subthreshold Regime                                |  |  |

| Xiaoyuan<br>Wang | Design of the tri-valued memristor and its application                                                                            |  |  |

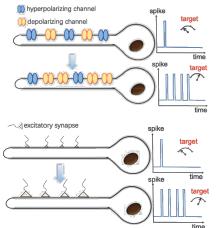

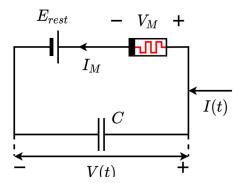

| Xinming Shi      | Memristor-based Integrate-and-Fire with Homeostatic Plasticity for Simulation and Application                                     |  |  |

| Yanzhen He       | Memimpedance-based Neural Adaptation Circuit with Hybrid CMOS/Volatile<br>Memristor LIF Neuron                                    |  |  |

| Yeon Jun<br>Kim  | Effects of Surface Defect States on Memristive Switching in InP/ZnSe/ZnS<br>Quantum Dot-based Memristors                          |  |  |

| YEUNWOO<br>KWON  | Effect of molecular alignment on off current and switching properties in PEDOT:PSS-based RRAM                                     |  |  |

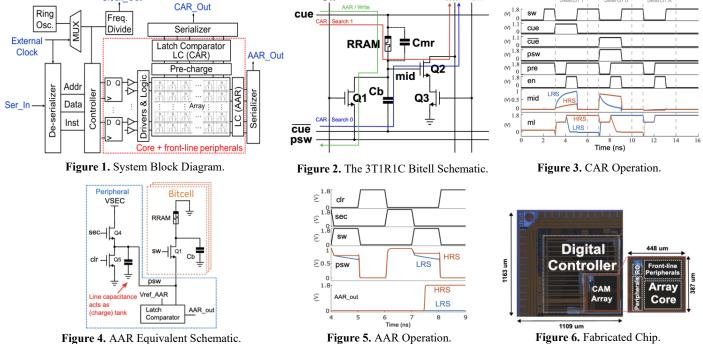

| Yihan Pan        | Energy-Efficient Capacitive-RRAM Dually Addressable Read Memory Core                                                              |  |  |

| Yoonho Cho       | Synaptic Behavior Implementation in a Highly Uniform Self-Rectifying Interfacial<br>Memristor                                     |  |  |

| Yuan Fa          | Volatile and Nonvolatile Resistive Switching in Wafer-Scale MoS2-based<br>Memristors                                              |  |  |

| Yujin Kim        | Analysis of 3-Dimensional Gate-Injection Field Effect Transistor with VNAND<br>Structure for Area-Efficient Neuromorphic Hardware |  |  |

# Analog weight update by tunable interfacial energy barrier by Li ion redistribution in Pt/p-LiCoO<sub>x</sub>/p-NiO/Pt memristor for neuromorphic computing

Boyoung Jeong<sup>1</sup>, Peter Hayoung Chung<sup>1</sup>, Jimin Han<sup>2</sup>, Taeyun Noh<sup>1</sup>, and Tae-Sik Yoon<sup>1,2\*</sup>

<sup>1</sup>[Graduate School of Semiconductor Materials and Devices Engineering, Ulsan National Institute of Science and Technology,

Republic of Korea]

<sup>2</sup>[Department of Materials Science and Engineering, Ulsan National Institute of Science and Technology, Republic of Korea] \*E-mail: [tsyoon@unist.ac.kr]

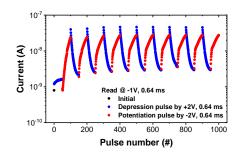

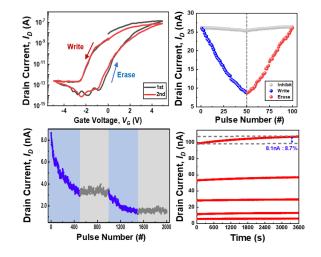

As the data-centric application, such as artificial intelligence, autonomous driving system and IoT, the demand for novel computing architecture increases due to the von Neumann bottleneck problems. From this point of view, neuromorphic computing is one of the promising new architectures. Neuromorphic computing emulates the human brain, which excels in complex tasks [1]. Unlike digital type computation in modern computer, neuromorphic computing employs analog synaptic weight for inference and learning process. To realize neuromorphic computing, artificial synapses which are essential elements for neuromorphic computing have been extensively investigated. For energy-efficient and high accuracy neuromorphic computing, a highly linear and symmetric weight update is important during potentiation and depression operation. Among the various candidates for artificial synaptic devices, two-terminal interface-type memristor is one of the promising devices due to its similar structure with biological neuron-synapse-neuron structure and precise and gradual resistance change in an analog manner [2]. In this study, Pt/p-LiCoO<sub>x</sub>/p-NiO/Pt memristor is proposed as an artificial synapse for application to neuromorphic computing. This device employed p-type oxides and a high work function electrode (ex. Pt) to construct a low interfacial energy barrier to mitigate abrupt conductance change. In addition, fast and movable Li<sup>+</sup> ions were used to modulate the interface energy barrier between NiO and Pt bottom electrode. Using p-type oxides and fast movable Li<sup>+</sup> ions working as dopants, the device shows the highly linear and symmetric analog change in conductance at a low voltage with a high speed. Beside the linear and symmetric weight update, the memristor shows various synaptic behaviors such as dependence of weight update on the number of pulse application, paired pulse facilitation, and short-term and long-term plasticity. The conductance modulation is induced by the tunable interface energy barrier at NiO layer and Pt bottom electrode by redistribution of Li<sup>+</sup> ions within the NiO layer as well as supplied Li<sup>+</sup> ions from LiCoO<sub>x</sub> layer. These results demonstrate the potential application of Pt/LiCoOx/NiO/Pt memristor to artificial synapses operated by voltagedriven Li<sup>+</sup> ion redistribution under the low energy barrier, realizing highly linear and symmetric weight update with a low voltage and high speed for energy-efficient neuromorphic computing systems.

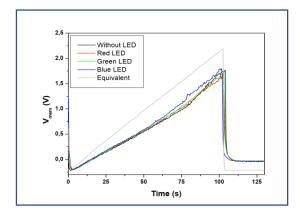

Figure 1. Weight update results of Pt/LiCoO<sub>x</sub>/NiO/Pt memristor

- [1] J. Tang et al. Adv. Mater., **31**, 1902761, 2019

- [2] Q. Wan et al. Adv. Mater. Technol., 4, 1900037, 2019

Figure 2. Operation speed; monitoring current change in real time during weight update

### Heterogeneous Density-based Clustering with Dual-functional Memristive Array

Dong Hoon Shin<sup>1</sup>, Sunwoo Cheong<sup>1</sup>, Néstor Ghenzi<sup>1, 2, \*</sup>, and Cheol Seong Hwang<sup>1, \*</sup>

<sup>1</sup>[Department of Materials Science and Engineering and Inter-university Semiconductor Research Center, College of Engineering,

Seoul National University, Seoul, 08826, Republic of Korea]

<sup>2</sup>[Universidad de Avellaneda UNDAV and Consejo Nacional de Investigaciones Científicas y Técnicas (CONICET), Mario Bravo

1460, Avellaneda, Buenos Aires 1872, Argentina]

\*E-mail: [nghenzi@snu.ac.kr, cheolsh@snu.ac.kr]

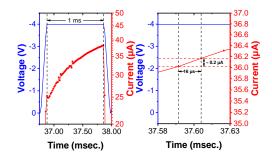

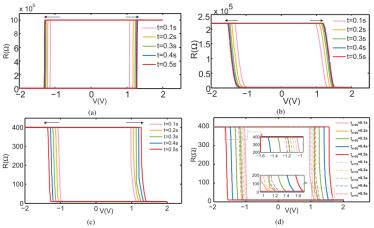

Recent data mining studies utilizing memristor-based crossbar arrays (CBAs) have employed various algorithms, including local hashing, data clustering, and dimensionality reduction. By leveraging the parallel vector-matrix multiplication (VMM) capabilities of CBAs, these systems operate more efficiently than traditional computing. However, previous studies faced limitations in fully implementing specific algorithms due to constrained device-level functionality. The data for these algorithms may have an analog or digital format, each requiring appropriate computing methods. This study proposes a new data clustering algorithm to overcome device- and algorithm-level limitations by fully utilizing the reconfigurable dual-mode (digital and analog) memristive CBA.

Conventional data clustering methods, such as k-means clustering and DBSCAN, inherently involve substantial computational overhead and struggle to effectively address local density variations within the data. To address this problem, this work introduces a new heterogeneous density-based clustering (HDC) algorithm to efficiently cluster datasets with varying densities using the parallel VMM operation of dual-functional CBAs. The processing method varies between analog and digital modes for data clustering on heterogeneous density datasets. In the analog mode, the Euclidean distance (ED) within the dataset is used to compute the local outlier factor (LOF) through analog domain VMM, enabling the detection of outliers. In contrast, the digital mode identifies clusters by evaluating connectivity between the detected outliers using digital domain VMM, thus considering local density in the clustering process. The proposed hardware-software co-developed algorithm feasibly clustered diverse synthetic datasets (~0.9 in adjusted rand index) that were impossible through conventional clustering algorithms. The protein structure was effectively confirmed using the single molecule localization microscopy (SMLM) dataset with various densities, demonstrating efficacy with real-world datasets. This study paves the way for efficient data clustering hardware in materials research, marking a significant advancement in the in-memory computing era.

Figure 1. The dual-mode CBA characteristics and VMM operations. (a) Reconfigurable digital and analog mode characteristics. (b) State variation of digital mode and state tunability of analog mode. Implementation of (c) analog domain VMM for ED and LOF calculation and (d) digital domain VMM for locality-considered data clustering with proposed bidirectional propagation clustering method.

#### References

[1] Sunwoo Cheong et al., Advanced Functional Materials, 34, 09108, 2023

# **Memimpedance-based Neural Adaptation Circuit** with Hybrid CMOS/Volatile Memristor LIF Neuron

Guoyang Huang<sup>1</sup>, Yanzhen He<sup>1\*</sup>, Deepika Yadav<sup>1</sup> and Themis Prodromakis<sup>1</sup> <sup>1</sup>[Centre for Electronics Frontiers, School of Engineering, University of Edinburgh, UK] \*E-mail: [y.he-114@sms.ed.ac.uk]

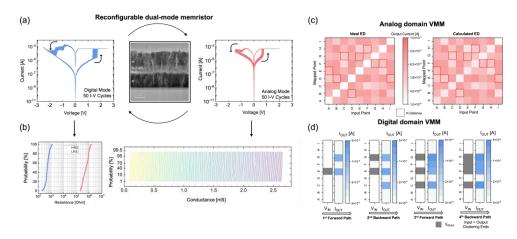

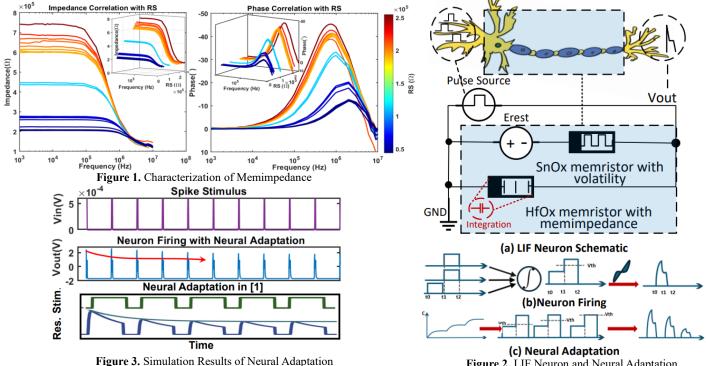

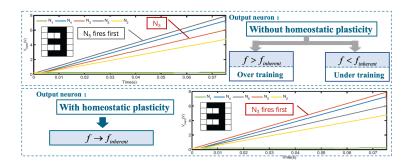

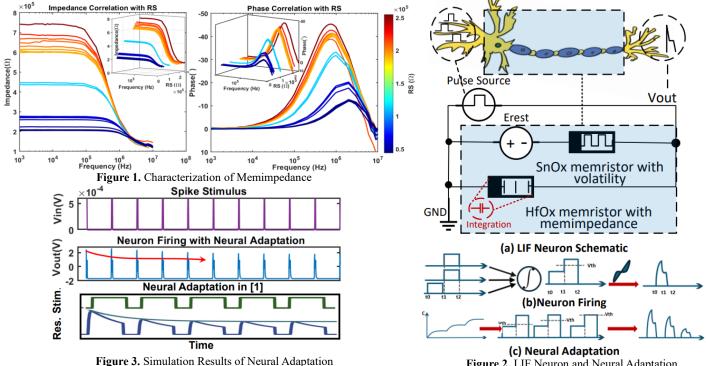

Neural adaptation, allowing neurons to dynamically adjust their responses based on stimuli, significantly contributes to predictive coding, enhancing environmental selectivity, and maintaining neural systems at the edge of chaos <sup>[1]</sup>, etc. The implementation of neural adaptation has aroused wide interest <sup>[2]</sup>; however, efficient implementation in hardware remains a challenge. In this paper, we propose a novel hardware implementation of neural adaptation based on hybrid CMOS/volatile memristor Leaky Integrate-and-Fire (LIF) Neuron Model, utilizing the observed memimpedance effect of memristors.

In Fig.1, we performed characterization for the memimpedance effect of our in-house fabricated HfOx-based memristors, using Keithley 4200A to realize specialized characterization pattern. The characterization flow includes two phases: 1. Applying multiple identical programming pulses to drive the memristor to different resistive state (RS). 2. Subsequently, applying a small AC signal of 0.5V, sweeping the frequency from 1kHz to 10MHz. RS is defined as the resistance under read pulses of 0.5V, preventing the device from switching. The cycle formed by the two phases is applied repeatedly, sweeping the voltage of the programming pulses in the first phase from 0.5V, 1V, 1.5V, ..., 6V, -0.5V, -1V, -1.5V, ..., -6V. The characterization results in Fig.1 are similar to the observation<sup>[3]</sup>, where we can observe a clear positive correlation between RS and the capacitance in the memimpedance. In Fig. 2(a), the pulse source of the LIF neuron represents the input current received by the presynaptic membrane, while the Vout corresponds to the neuron spikes generated at the postsynaptic membrane. The current pulses integrated in the capacitor cause the Vout exceed the Vth of SnOx-based memristor, leading to the abruptly decrease in its RS and the Vout, forming a whole spike, as shown in Fig. 2(b). The spike is then propagating to the subsequent neuron. To realize neural adaptation, we replace the capacitor for integration in the LIF neuron with the HfOx-based memristor, to utilize the characterized memimpedance features for the integration with a time-varying integral coefficient (Capacitance). It allows the membrane Vth gradually to increase, leading to a progressively shorter output spikes until saturation. In Fig. 3, the simulation results in Cadence that is resemble to the biology neural adaptation <sup>[1]</sup> indicates the firing intensity descend with prolonged and repetitive stimuli.

Figure 2. LIF Neuron and Neural Adaptation

- [2] Ganguly, C. et al., Commun. Eng., 3(1), 22, 2024.

- [3] S. Yu et al., IEEE Int. Electron Devices Meet., 12.1.1-12.1.4, 2011.

<sup>[1]</sup> Benda, J., Curr. Biol., 31(2), R110-R116, 2021.

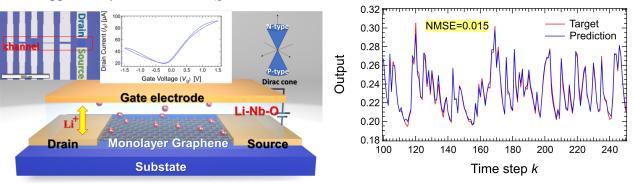

### Reservoir computing using graphene-based solid state electric double layer transistors

Hina Kitano<sup>1,2</sup>, Daiki Nishioka<sup>1</sup>, Wataru Namiki<sup>1</sup>, Tohru Higuchi<sup>2</sup>, Kazuya Terabe<sup>1</sup>, and Takashi Tsuchiya<sup>1</sup>

<sup>1</sup>Research Center for Materials Nanoarchitectonics, National Institute for Materials Science, JAPAN

<sup>2</sup>Department of Applied Physics, Tokyo University of Science, JAPAN

\*E-mail: TSUCHIYA.Takashi@nims.go.jp

Recently, the rapid development of AI technology has confronted serious problems such as increasing computational costs and increasing power consumption. Physical reservoir computing (PRC) is a form of physical implementation of machine learning that is suitable for efficiently processing time series data and has the possibility to resolve the problems. It utilizes nonlinear dynamics of physical phenomena in materials or devices for information processing. In this context, PRC has been studied using various physical phenomena such as optical response and magnetic spin. Previously, our team developed ion-gating reservoirs (IGRs) using solid-state ionic materials, such as electric double layer (EDL) and redox-based transistors.<sup>[1-5]</sup> In this study, we tackled improving the PRC performance of EDL transistor-based IGRs by focusing on the channel material.

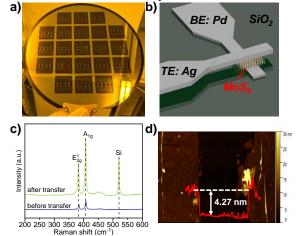

We used a monolayer graphene deposited by chemical vapor depositions as the channel semiconductor with Au/Cr source and drain electrodes. Then, an electric double layer transistor (EDLT) was fabricated by depositing a Li<sup>+</sup> -conducting amorphous solid electrolyte (Li-Nb-O) and a gate electrode (LiCoO<sub>2</sub>) by pulsed laser deposition, as shown in Fig.1. Applying various  $V_G$  to the gate electrode causes Li<sup>+</sup> transport inside the electrolyte. The formation of EDL at the graphene channel/electrolyte interface changes the electron carrier density in graphene, and the  $I_D$  through the channel can thus be controlled. We evaluated the electrical characteristics of this transistor and its performance as a PRC device through a benchmark task.

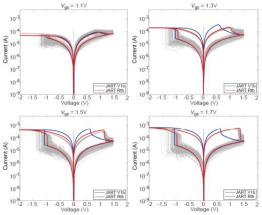

The  $I_{\rm D}$ - $V_{\rm G}$  characteristic measured by sweeping the  $V_{\rm G}$  from -1.5 V to +1.5 V is shown in Fig. 1. When a negative  $V_{\rm G}$  is increased (e.g.,  $V_{\rm G} < -0.2$  V), Li <sup>+</sup> moves toward the gate electrode, and holes are injected into the channel surface, forming an EDL (p-type conduction) and vice versa. The performance of this EDLT was evaluated by the 2nd-order nonlinear autoregressive moving average (NARMA2) task, which is a time-series data prediction task requiring nonlinearity and short-term memory and is thus widely used as a typical benchmark task of PRC. The performance is evaluated by the value of the normalized mean square error (NMSE) with the nonlinear transform output (predicted waveform) of the PRC and the target (i.e., a low NMSE means high performance). The predicted waveform by the EDLT reproduced the characteristics of the target waveform well (Fig.2), indicating that it predicted the time-series data with high accuracy. The NMSE (the test phase) was 0.015, which was notably lowered by 40% compared to the high-performance diamond-EDLT (NMSE: 0.020 in the test phase) <sup>[1]</sup> The high performance is attributed to the unique  $I_{\rm D}$ - $V_{\rm G}$  and transient characteristic of the ambipolar EDLT. This work was supported by JST PRESTO (grant number, JPMJPR23H4).

Figure 2. Target and prediction waveforms of the NARMA2 task

### References

[1] D. Nishioka, et al., *Sci. Adv.* 8, eade1156 (2022). [2] T. Wada et al., *Adv. Intell. Syst.* 5, 2300123 (2023). [3] K. Shibata et al., *Sci. Rep.* 13, 21060 (2023). [4] Y. Yamaguchi et al., *Appl. Phys. Express*, 17, 024501 (2024). [5] D. Nishioka et al., *Sci. Adv.* 10, eadk6438 (2024).

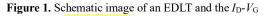

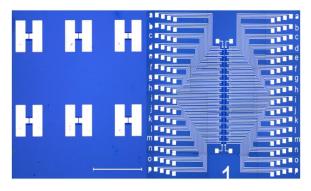

# Neuromorphic Computing based on Two-terminal Au nanoparticle Floatinggate Memristor

Hongwoon Yun 1<sup>1</sup>, Woo Jong Yu 2<sup>1,\*</sup>

<sup>1</sup>[Department of AI System Engineering, Sungkyunkwan University, Korea]

\*E-mail: [miccro21@skku.edu]

The majority of computers have been built based on the von Neumann architecture because it has powerful advantages. However, with the advent of the big data era, von Neumann bottleneck occurs due to the limitations of the physical structure. Neuromorphic computing, which mimics human brain function by creating a circuit that mimics the shape of neurons, is one of the ways to solve the above problem.

In this study, we demonstrated Neurosynaptic array based on two-terminal au nanoparticle floating-gate Memristor (AuNp-FGM). By forming au nanoparticles between tunneling oxide and floating gate, the device

can operate lower than ±3V region. Using the change of the fermi level (Ef) of graphene, AuNp-FGM exhibits

memory characteristics. The device exhibits high on/off ratio over than 107, retention longer than 9 hours, and robust endurance more than 80,000 times. Also, AuNp-FGM shows low cycle to cycle variability of  $C_v = 3.6\%$  (n=90,  $C_v = \sigma/\mu$ ,  $\sigma$  = standard deviation,  $\mu$  = mean value). Furthermore, AuNp-FGM shows almost linear update characteristics, for 100 level potentiation (+4V, 0.4s), nonlinearity factor ranged from 0.1 to 0.6. For 100 level depression (-3V, 0.2s), it ranged from 2.3 to 4.6 (n = 15), indicating excellent applicability for neuromorphic computing. A similar trend was also observed even when the number of input pulses was changed (50, 100, 200, 300, 400 inputs)

Based on AuNp-FGM, we fabricated a neurosynaptic array, consisting of 18 neurons and 288 synapses. Four types of data ('A', 'B', 'Y', 'Z') were used in 90 times learning simulation, 2 neurons and 32 synapses were used to learn one alphabet. The training results were confirmed by measuring the output current of the neurons which is connected to the trained synapses, we were able to successfully trained each alphabet on the neurosynaptic array.

Figure 1. OM image of AuNp-FGM (left, scale bar = 1mm), OM image of Neurosynaptic array (right)

- [1] Vu, Q., et al., Nat. Commun. 7, 12725 (2016).

- [2] Q. A. Vu, et al., Adv. Mater. 2017, 29, 1703363.

- [3] Won, U.Y., Nat. Commun. 14, 3070 (2023).

Figure 2.  $I_{ds}$ - $V_{ds}$  characteristic of AuNp-FGM

Artificial retina technology plays a crucial role in the field of artificial intelligence, particularly in the domains of fast static target recognition and trajectory detection. However, the current challenge lies in the absence of highly sensitive, reconfigurable, and large-scale integrated retinal devices, hindering the development of fully functional artificial retinal hardware. In this study, we introduce a groundbreaking monolithically integrated 409600 pixel perovskite optoelectronic sensor array. By utilizing indium gallium zinc oxide thin film transistors and perovskite photodetectors to mimic the anatomical structure of the biological retina, we have achieved a 1T-1PD pixel with broadband and reconfigurable characteristics. Notably, this structure demonstrates rapid photoelectric response capabilities under reverse-biased conditions for sensitive photoelectric detection tasks, while exhibiting continuous photoconductivity effects in forward-biased mode for trajectory tracking detection tasks.

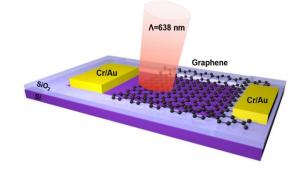

# Silicon/Graphene Optical Sensors and Neuromorphic system for Visual Cell Emulation

Hyungsuk Oh 1<sup>1</sup>, Woo Jong Yu 2<sup>2</sup>

<sup>1</sup>[Department of AI System Engineering, Sungkyunkwan University, Republic of Korea]

<sup>2</sup>[Department of Electrical and Computer Engineering, Sungkyunkwan University, Republic of Korea]

\*E-mail: [micco21@skku.edu]

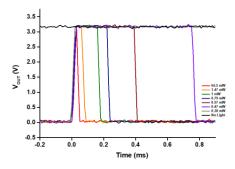

In the field of solar energy, next-generation Schottky solar cells incorporating graphene, a two-dimensional material, are gaining significant attention due to their high efficiency and open-circuit voltage (VOC)<sup>[1]</sup>. The unique ability of graphene-based solar cell devices to convert light into electrical energy positions them as ideal candidates for replicating the functionality of human visual cells<sup>[2]</sup>.

candidates for replicating the functionality of human visual cells <sup>121</sup>. This study investigates the creation of a biomimetic device that emulates the complex processes of the human retina, including the formation of visual information, its conversion into electrical signals by photoreceptors, and the subsequent transmission of these signals to the brain via the optic nerve. The device aims to simulate the visual cortex's role in object recognition. By integrating a comparator, we achieve a hardware component of the vision neural network, where the modulation of spike numbers in response to varying light intensities mimics the human perception adjustment (Figure 1). The simulation of the visual cortex's function was conducted using Conventional Neural Network (CNN) modeling in MATLAB. The simulations employed the MNIST dataset (pixel size: 28x28) to compare the performance of existing analog and digital signals, achieving a peak accuracy of approximately 75% after

modeling in MATLAB. The simulations employed the MNIST dataset (pixel size: 28x28) to compare the performance of existing analog and digital signals, achieving a peak accuracy of approximately 75% after thirteen iterations (Figure 2). This study demonstrates the feasibility of a neuromorphic integrated visual system that closely mimics the human visual system. Building upon this foundation, future research will focus on developing an advanced visual system that operates similarly to the human brain by connecting our own floating gate memristor to the visual sensor described in this study <sup>[3]</sup>. The spike information generated by the visual sensor will be transmitted to the memristor, following the principles of spike-timing-dependent plasticity (STDP), instead of using a comparator. Memristors have the capability to learn and store transmitted information, functioning akin to real neurons through the leaky integrate-and-fire (LIF) mechanism.

Figure 1. Output spikes according to the laser intensity

Figure 2. Schematic image of Silicon/Graphene Optical Sensor

Figure 3. Schematic image of SNN system using the 28\*28 MNIST dataset

- [1] Won, Ui Yeon, et al. Nano Research 14, 1967-1972, 2021

- [2] Mueller, Thomas, Fengnian Xia, and Phaedon Avouris. Nature photonics 4.5, 297-301, 2010

- [3] Won, Ui Yeon, et al. Nature Communications 14.1, 3070, 2023

### Physical Reservoir Computing with Percolating Networks of Nanoparticles

Jamie Steel<sup>1</sup>, Joshua Mallinson<sup>1</sup> and Simon Brown<sup>1</sup>

<sup>1</sup>[School of Physical and Chemical Sciences, University of Canterbury, Aotearoa New Zealand] \*E-mail: [jamie.steel@pg.canterbury.ac.nz]

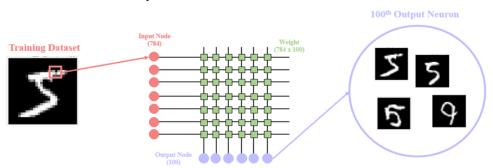

The network of neurons and synapses that comprises the biological brain enables natural information processing with remarkable efficiency [1]. Percolating Networks of Nanoparticles (PNNs) consisting of metallic nanoparticles (Figure 1) are complex self-assembled nanoscale systems that possess many brain-like attributes

and are therefore appealing for neuromorphic computation [2]. Additionally, PNNs are fabricated with straightforward cost-effective processes and have remarkable longevity [3].

Previously we have shown via simulations that PNNs, constructed from networks of memristive tunnel-gaps and acting as reservoirs within a reservoir computing (RC) framework, can successfully perform computational tasks such as NARMA, Memory Capacity, Non-linear Transformation, and Waveform Discrimination [4]. Here, we demonstrate experimentally that our PNNs solve the more practically relevant task of

spoken digit recognition. After suitable pre-processing steps, our PNN

transforms signals to a higher dimensional space, allowing prediction of

the spoken digit. We achieve a high classification accuracy on the TI-46

physical RC systems. We further show that our system achieves state-of-

dataset [5], comparable with the best performance achieved with other

Figure 1. Schematic of a Percolating Network of Nanoparticles (PNN) with multiple gold electrodes. The different particle colours represent individual groups of well-connected particles separated by memristive tunnel gaps.

the-art accuracy on the larger and more challenging Free Spoken Digit Dataset (Figure 2).

**Figure 2.** Spoken Digit Recognition. (a-c) Preparation of the spoken digits to an appropriate signal for our PNN. (d) The transformed signal measured from the PNN. (e-h) Final classification accuracy of the spoken digits.

- [1] E. Kandel, et al., Principles of Neural Science, 5th ed. McGraw-Hill, 2013

- [2] J. Mallinson, et al., Sci. Adv., 5(11), eaaw8438, 2019

- [3] S. Bose, et al., IEEE Trans. Electron Devices, 64(12), 5194-5201, 2017

- [4] J. Mallinson, et al., Nanoscale, **15**(22), 9663-9674, 2023

- [5] J. Mallinson, et al., Adv. Mater, 2402319, 2024

### **Cluster type selector-less 1R memristor array for spiking neural network**

Ji Eun Kim<sup>1,2</sup>, Ju Young Kwon<sup>1</sup>, Suk Yeop Chun<sup>1,3</sup>, Keunho Soh<sup>1,2</sup>, Sahn Nahm<sup>2,3</sup> and Jung Ho Yoon<sup>4\*</sup> <sup>1</sup>[Electronic Materials Research Center, Korea Institute of Science and Technology (KIST), Seoul 02791 Republic of Korea] <sup>2</sup>[Department of Materials Science and Engineering, Korea University, Seoul 02841, Republic of Korea] <sup>3</sup>[KU-KIST Graduate School of Converging Science and Technology, Korea University, Seoul 02841, Republic of Korea] <sup>4</sup>[School of Advanced Materials Science and Engineering, Sungkyunkwan University, Suwon 16419, South Korea]

### \*E-mail: [junghoyoon@skku.edu]

A memristor holds great potential as a next-generation device, but device-level performance improvements and large-scale array implementation are necessary for various emerging applications. The switching characteristics and performance of memristors are predominantly determined by mobile species or redox reactions and the consequent formation of conductive paths. However, controlling the redox reaction is challenging, making it difficult to manage the precise growth and rupture of the conductive path, significantly degrading the switching characteristics. Furthermore, the well-known conventional ion-based switching behavior does not have inherent non-linearity due to the formation of continuous conductive filaments, so further development of an external selection device and verification of its compatibility are required, which makes the practical application of memristor arrays difficult.

Therefore, in this study, we propose a nanorod-based memristor, Pt/SiO<sub>2</sub> nanorods/Ru, to enhance switching characteristics by controlling the ion dynamics, such as activation energy, mobility, and redox reaction. By introducing a nanorod structure, the dominant movement towards the surface with relatively lower activation energy for diffusion leads to increased mobility, and the concentration of electric fields due to structural characteristics promotes redox reactions. This approach leads to efficient ionization and increased ion mobility, resulting in electroforming-free operation, low power consumption, and high uniformity. Additionally, the ion supply can be precisely controlled, enabling high linearity in conductance modulation and forming the different types of conductive paths from the conventional filamentary memristor, leading to inherent non-linearity in the On-state. These memristors were successfully integrated into a 16 x 16 selector-less crossbar array, demonstrating high uniformity and an 80% MNIST recognition accuracy when simulated using a Spiking Neural Network (SNN), underscoring their potential for efficient neuromorphic computing and AI applications.

# Energy efficient, high performance resistive memory device with Ag/VO<sub>x</sub>/Pt structure by facilitated Ag filament formation

Jiyeon Ryu<sup>1</sup>, Kitae Park<sup>1</sup>, and Tae-Sik Yoon<sup>1,2\*</sup>

<sup>1</sup>Graduate School of Semiconductor Materials and Devices Engineering, Ulsan National Institute of Science and Technology, Ulsan 44919, Republic of Korea

<sup>2</sup>Department of Materials Science and Engineering, Ulsan National Institute of Science and Technology, Ulsan 44919, Republic of

Korea

\*E-mail: tsyoon@unist.ac.kr

Nowadays, conventional von Neumann computing systems face significant bottlenecks in processing speed due to data assessment between processor and storage for data-intensive applications. The data movement including the transfer from off-chip to on-chip incurs substantial costs in terms of bandwidth, energy, and latency—far more than computation itself. Furthermore, energy consumption is a major constraint in the conventional computing systems. These issues are especially pronounced in today's data-intensive servers and mobile systems. In addition, conventional memory device technology is facing numerous challenges in technology node scaling, reliability, energy efficiency, and performance enhancement. Thus, breakthroughs in memory devices for new computing systems are highly required. In these circumstances, emerging non-volatile memories (NVMs) such as resistive random-access memory (RRAM) are gaining attention for their potential as computing elements in processing-in-memory (PIM) systems, due to their potential simple structure and high performance. To achieve high performance and reliability in RRAM devices, it is crucial to explore suitable switching oxide materials and structural modulations.

Among various oxides for RRAM, vanadium oxide  $(VO_x)$  exhibits proper properties as resistive switching element such as high metal cation diffusivity such as Li<sup>+</sup>, Zn<sup>2+</sup>, Na<sup>+</sup>, K<sup>+</sup> ions. As well as it enables to serve as a great cathode material in both crystalline and amorphous phase for the lithium-ion batteries (LIBs) or aqueous zinc-ion batteries (aqZIBs) [1–5], it can make vanadium oxide promising electrolyte for metal filament-type RRAM operating through the formation and dissolution of conductive filaments consisting of metal atoms within a solid electrolyte.

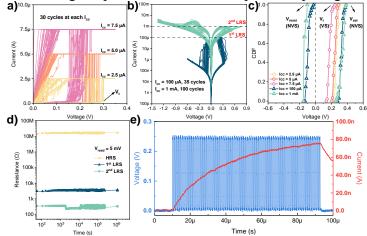

In this study, the resistive switching properties of Ag/VO<sub>x</sub>/Pt structured device is investigated for the application to high performance computing systems. DC voltage sweep measurements reveals average V<sub>SET</sub> and V<sub>RESET</sub> values of +0.23 V and -0.07 V respectively, with a low IRESET of less than 1 mA, along with forming-free characteristic. The switching speed is less than 100 ns in pulse measurements. Furthermore, the device exhibits narrow cell-to-cell (C-C) and device-to-device (D-D) distributions. Almost complete retention for more than 12 hours at room temperature is achieved. These features-forming-free, low operation voltage, fast operation speed, uniform cyclability, and long memory retention-can take advantages when this device is implemented as processing elements in PIM architecture. In addition to enhanced electrical properties, a noticeable two-step resistance change is observed at SET pulse operation. Upon the application of SET pulse, the resistance partially decreases to middle resistance state (i.e., transient resistance state). After several hundred nanoseconds, it further decreases to reach the low resistance state once the filament formation is complete. The two-step resistance change in a staircase-like form is interpreted to be associated with the clustering of Ag atoms within  $VO_x$  layer followed by Ag filament formation. The facilitated formation and rupture of Ag filament within an oxygen-deficient  $VO_x$ layer eliminates the need for a forming step. Moreover, the amorphous structure of  $VO_x$  layer, abundant with oxygen vacancies, significantly enhances Ag<sup>+</sup> ion migration, thereby facilitating filament formation and stabilizing uniformity. These results highlight the potential of Ag/VO<sub>x</sub>/Pt device as non-volatile computing elements which is suitable for PIM applications.

<sup>[1]</sup> Kulish, V. V. et al., RSC Adv. 7(30), 18643-18649, 2017

<sup>[2]</sup> Mattelaer, F. et al., ACS Appl. Mater. & Interfaces, 9(15), 13121-13131, 2017

<sup>[3]</sup> Kumagai, N. et al., *Electrochemistry*, 72(4), 261-265, 2004

<sup>[4]</sup> Ju, B. et al,. Chem. Eng. J, 420(3), 130528, 2021

<sup>[5]</sup> Chen, S. et al,. Chem. Eng. J, 403, 126380, 2021

### Stochastic Ion-motion Mediated Volatile Threshold Switching Memristor Enables Probabilistic Computing

Keunho Soh<sup>1,2</sup>, Ji Eun Kim<sup>1,2</sup>, Suk Yeop Chun<sup>1,3</sup>, and Jung Ho Yoon<sup>4\*</sup>

<sup>1</sup>[Electronic Materials Research Center, Korea Institute of Science and Technology (KIST), Republic of Korea]

<sup>2</sup>[Department of Materials Science and Engineering, Korea University, Republic of Korea]

<sup>3</sup>[KU-KIST Graduate School of Converging Science and Technology, Korea University, Republic of Korea]

<sup>4</sup>[School of Advanced Materials and Engineering, Sungkyunkwan University (SKKU), Republic of Korea]

\*E-mail: [junghoyoon@skku.edu]

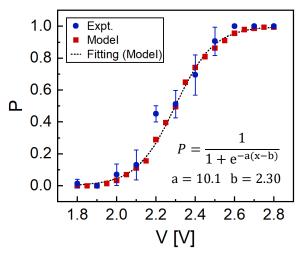

Recently, quantum annealing (QA) machine has been utilized to solve combinatorial optimization problems (COPs), which typically exhibits exponential time complexity, within a reasonable scale of execution time. Despite the dramatic improvement in problem-solving capability offered by QA, extremely low temperatures for operation, leading to high power consumption and operational difficulties are pointed out as critical disadvantages. To breakthrough aforementioned drawbacks, probabilistic computing has been proposed as an attractive approach to solving COPs by mimicking QA at room-temperature using the probabilistic output of electronic devices. For its implementation, it is essential to develop devices that are inherently stochastic and capable of generating outputs at high speed with a probabilistic bit (p-bit), which includes the device and refines its output, is necessary. However, reported implementations of probabilistic computing with p-bit so far involve devices with complex structure and additional component such as transistor, or demonstrate simulations based on the characteristics of a single p-bit.

Meanwhile, we note that ion-motion mediated memristors with volatile threshold switching (TS) characteristics demonstrate significant cycle-to-cycle (C2C) variation under the applied arbitrary pulse train. Moreover, the device's turn-on probability increases proportional to the pulse amplitude. This behavior occurs because an increase in electrical bias accelerates ion-motion, causing the conductive path inside the device to grow without precise confinement of formation spot. Therefore, this bias-dependent controllable probability and stochastic property make TS devices one of the most promising candidates for a p-bit.

In this study, we fabricated a vertical Metal-Insulator-Metal (MIM) structure TS device using Pt/Ag/SiO<sub>2</sub>/Ag/Pt. The device exhibits a low threshold voltage ( $\approx \pm 0.2$  V) with C2C variation, an ultra-low OFF state current (< 10 pA), and a high ON/OFF ratio (> 10<sup>7</sup>). Furthermore, by adopting a nanorods-based (NRs) switching layer, we achieved remarkable switching speed improvement, which contributes to a higher bit generation rate for the TS-based p-bit. Additionally, it was confirmed that the generated probabilistic output depends on the amplitude of the input pulse, successfully forming a sigmoid fitting curve, a representative characteristic for application in probabilistic computing. It is believed that the NRs-TS device and the accompanying p-bit shown in this work are suitable for low-power and high-speed probabilistic computing applications.

### Size-Dependent Study on Nanosized VO<sub>2</sub> Phase Change Memory Devices.

László Pósa<sup>1,2</sup>\*, Lóránt Bakos<sup>2</sup>, Tímea Nóra Török<sup>1,2</sup>, Zsigmond Pollner<sup>2</sup>, Miklós Csontos<sup>3</sup>, Sebastian Werner Schmid<sup>2</sup>, János Volk<sup>1</sup> and András Halbritter<sup>2</sup>

<sup>1</sup>Institute of Technical Physics and Materials Science, Centre for Energy Research, Budapest, HUNGARY

<sup>2</sup>Department of Physics, Institute of Physics, Budapest University of Technology and Economics, Budapest, HUNGARY

<sup>3</sup>Institute of Electromagnetic Fields, ETH Zurich, Zürich, SWITZERLAND

\*E-mail: [posa.laszlo@ek.hun-ren.hu]

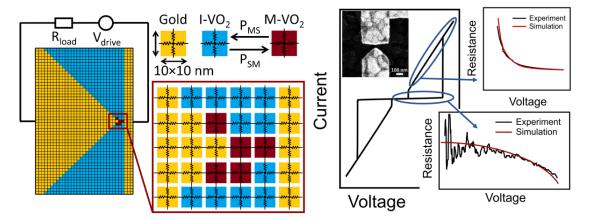

Volatile Mott memristors are key components of neuromorphic circuits alongside conventional non-volatile resistive switches. While the latter essentially plays the role of artificial synapses in neural network applications, the former act as artificial neurons implementing several neural spiking patterns [1]. In addition, Mott memristors are well applied to oscillating neural networks, where information processing occurs in the dynamic domain, and the computation is encoded by the phase of the oscillators, all these applications require fast operation. In our study, we fabricated devices with varying ultrasmall ( $\approx 20-100 \text{ nm}$ ) spacing between the contacting electrodes. The asymmetric, V-shaped electrode arrangement focuses the switching region into a well-defined spot [2], enabling us to analyze the device operation as a function of the device size. By applying time-resolved measurements, we also revealed the switching dynamics. switching dynamics. The simplified spatial structure of the active volume also facilitates the device modeling. From this inspiration, a two-dimensional resistor network model was employed to simulate the size-dependent and dynamic behavior of our nanosized VO<sub>2</sub> memory devices.

Figure 1. Left panel: Schematic of our two-dimensional resistor network model using realistic electrode geometry. The active region is modeled as an array of cells, each of which can be either insulating (I-VO2, blue) or metallic (M-VO2, red) state. The phase transition is considered a thermally activated process, with transition probabilities of the cells ( $P_{IM}$  (T) and  $P_{MI}$  (T)) depending on the temperature. **Right panel:** Switching I(V) trace of the nanogap device. The two inset panels show the measured (black curves) and simulated (red curves) R(V) characteristics of high resistance OFF state (bottom panel) and low resistance ON state (top panel).

- [1] Yi, W. et al., NatureCommunications 9, 4661925 (2018)

- [2] Pósa, L. et al, ACS Applied Nano Materials, 6, 9137 (2023)

### Improved Stateful Logic Designs based on Memristive 1T-1R Arrays

Leon Brackmann<sup>1</sup>, Tobias Ziegler<sup>1</sup>, Mahdi Najjar<sup>1</sup>, Stephan Menzel<sup>2</sup> and Dirk J. Wouters<sup>1</sup>

<sup>1</sup>Chair of Materials of Electrical Engineering II and Institute of Materials of Electrical Engineering, RWTH Aachen University,

GERMANY

<sup>2</sup>Peter-Grünberg Institute 7, Forschungszentrum Juelich GmbH, GERMANY

\*E-mail: l.brackmann@iwe.rwth-aachen.de

Memristive Devices have recently gained attraction for the implementation of Computing-in-Memory (CIM) and especially their potential in stateful logic concepts such as Memristor-Aided Logic (MAGIC). Originally proposed for passive crossbar structures, modern concepts integrate these operations by combining memristive elements together with traditional CMOS transistors, which improves the reliability regarding sneak path currents. However, as stateful memristive concepts rely on the conditional switching of a memristive device, they are prone to variability, which arises from the inherent memristive switching mechanism and its stochasticity. Additionally, the high amount of operation parameters, namely pulse voltages/duration, initial resistances states, logic inputs and the switching polarity, further increase the complexity of the operation.

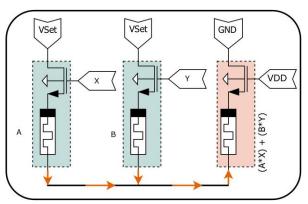

To address these challenges, we introduce a robust framework to evaluate the switching-dependent error rates of stateful memristive logic concepts focusing on active 1T-1R structures [1]. Based on the framework results, we identify critical operations parameters and, for the first time to our knowledge, we demonstrated the successful execution of MAGIC operations in hafnium-based integrated 1T-1R devices. By adjusting the operation voltages, we achieved experimental operation success rates up to 100% [2].

Based on the observations of stateful logic in simulation and measurement, we propose two novel extensions for improving the original stateful MAGIC concept: 1) the combination of stateful and non-stateful logic elements for concatenated Boolean operations. Specifically in active 1T-1R structures, the transistor gate voltage can be exploited as second, volatile, input to tune the 1T-1R series resistance. This approach extends the number of logic inputs from 2 (stateful MAGIC) to 4 (combined stateful/non-stateful) per operation which significantly reduces the required number of cycles. 2) a 1T-1R Three-Memristor Stateful Logic approach, which extends the executable primitive logic functions with only a minimum of additional circuitry.

| Inputs | <b>SR</b><br>VSet 1.0 V<br>Vgate 1.5 V | <b>SR</b><br>VSet 1.2 V<br>Vgate 1.5 V | <b>SR</b><br>VSet 1.0 V<br>Vgate 1.7 V |

|--------|----------------------------------------|----------------------------------------|----------------------------------------|

| 00     | 0                                      | 0                                      | 0                                      |

| 01     | 38                                     | 41                                     | 100                                    |

| 10     | 55                                     | 27                                     | 99                                     |

| 11     | 94                                     | 88                                     | 100                                    |

Table 1. Experimental voltage-dependent 1T-1R

MAGIC success rates (SR)

Figure 1. Circuit Diagram for combined stateful (A,B) and non-stateful (X,Y) logic inputs as MAGIC extension

### References

Brackmann et al., *IEEE ITC-Asia, Taipei, Taiwan, 2022* Brackmann et al., *Adv. Intell. Syst.*, 6, 2300579, 2024

Funded by the German Research Foundation (SPP 2262) and the Federal Ministry of Education and Research (16ME0398K, 16ME0399 and 03ZU1106AA).

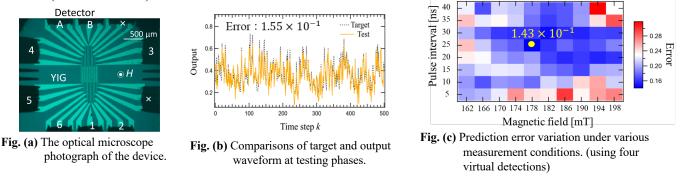

### Computational performance of Magnonic Reservoir Computing with Increased Number of Detectors

<sup>o</sup>Maki Nishimura<sup>1,2</sup>, Wataru Namiki<sup>1</sup>, Daiki Nishioka<sup>1</sup>,

Tohru Higuchi<sup>2</sup>, Kazuya Terabe<sup>1</sup>, and Takashi Tsuchiya<sup>1,2</sup>

<sup>1</sup>NIMS, <sup>2</sup>Tokyo Univ. of Sci.

E-mail: TSUCHIYA.Takashi@nims.go.jp

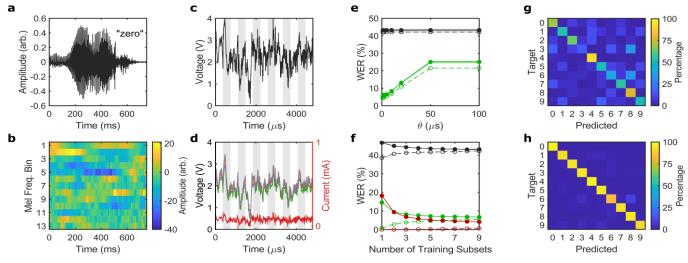

Reservoir computing addresses concerns over power consumption and computational costs in machine learning. It enables fast learning with low power consumption and computational costs. By using a device with nonlinearity, short-term memory, and high dimensionality, physical implementation is possible. In particular, it was theoretically predicted and experimentally verified that spin wave interference can perform highly efficient reservoir computing, demonstrating improved performance with up to two spin wave detectors.<sup>[1,2,3]</sup> Furthermore, while simulations have shown that increasing dimensionality through two or more multiple detections can improve computational performance,<sup>[4]</sup> the effects of using more than two detectors on the computational performance through high dimensionality enhancement remain unclear. In the study, we evaluated the computational performance experimentally by increasing the number of detectors to six and utilizing nonlinear interference effects.

We used a magnonic device with Y<sub>3</sub>F<sub>5</sub>O<sub>12</sub> single crystal, as shown in Fig. (a), to perform one of the most important prediction benchmark tasks from the Nonlinear Autoregressive Moving Average (NARMA) model. In this study, we increased the number of detectors to six to improve computational performance through a significant increase in the number of detections and experimental nonlinear interference effects. We evaluated the prediction error of NARMA10, which requires short-term memory up to 10 steps with the external applied magnetic field and input pulse interval as measurement conditions. First, to determine the two terminals used for input, we selected the two terminals from the six terminals indicated in Fig. (a) and conducted a total of 15 measurements. The detection terminals used were terminals A and B, as indicated in Fig. (a). As shown in Fig. (b), When terminals 3 and 5 were used as input terminals, the comparison between the target waveform and the output waveform during testing under the conditions of a magnetic field of 178 mT and a pulse interval of 25 ns shows a good match, at that time, the error was 0.155 during the testing phase. When the number of detections was virtually increased to four, as shown in Fig. (c), the computational performance changed with respect to the magnetic field and pulse interval, resulting in an improvement in the best score under the same conditions as with two detections. This work was partially supported by the Innovative Science and Technology Initiative for Security Grant Number JPJ004596, ATLA, Japan, and JST PRESTO (JPMJPR23H4).

[1] Nakane et al., IEEE Access 6, 4462 (2018). [2] Namiki et al., Adv. Intell. Syst. 5, 2300228 (2023).

[3] Namiki et al., Mater. Today Phys. 45, 101465 (2024). [4] Nakane et al., Phys. Rev. Appl. 19, 034047 (2023)

### Circuit emulating neuronal response based on Ga<sub>2</sub>O<sub>3</sub> photomemristors

M. Sparvoli<sup>1,2</sup>\*, F. O. Jorge<sup>1</sup>, D. G. Fidelis<sup>1</sup>, G. S. Gouvea<sup>1</sup>, R. D. Mansano<sup>3</sup>, A. F. Silva<sup>4</sup>, J. F. D. Chubaci<sup>1</sup> and J. A.

Freitas, Jr.5

<sup>1</sup>Instituto de Física, Universidade de São Paulo, Brasil

<sup>2</sup>Centro de Engenharia, Modelagem e Ciências Sociais Aplicadas, UFABC, Brasil

<sup>3</sup>Escola Politécnica, Universidade de São Paulo, Brasil

<sup>4</sup>Instituto de Física, Universidade Federal da Bahia, Brasil

<sup>5</sup>Naval Research Laboratory, Washington DC, USA

\*E-mail: marinsparvoli@yahoo.com.br

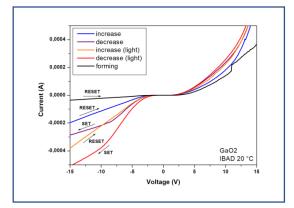

Gallium oxide-based memristors were introduced as component of a circuit emulating a neuronal membrane to investigate its nonlinear operation and sensitivity to electromagnetic radiation in the visible spectral region. While the former characteristics is employed on digital memory and logical circuit development, the latter has attracted interest for biological and neuromorphic system applications. Gallium oxide (Ga<sub>2</sub>O<sub>3</sub>), which has five main crystalline phases, is a transparent semiconductor material with band gap around 4.5 - 4.9 eV. It has been observed that substrate temperature plays an important role during the deposition process of thin films, such as crystal phase selectivity and optoelectronic properties [1]. In this work, testing devices were produced from films deposited, by IBAD (Ion Beam Assisted Deposition) on p-type Silicon substrates, at room temperature and ~400 °C. Aluminum contacts were evaporated over the thin film surface and on the substrate back surface. Films deposited at lower temperatures predominantly have  $\beta$ -phase, while those deposited at higher temperatures have dominant  $\varepsilon$ -phase, as verified by X-ray diffraction. The memristors were characterized by voltage-current analysis. The current-voltage measurement of isolated device provided key information for understanding the memristor operation, revealing its unipolar characteristic and responsiveness to light (Figure 1). Therefore, the tested devices are, in fact, photomemristors. In the neuromorphic circuit measurement, the aim is to use the circuit that emulates a neuronal membrane and study the memristors behavior. It was proved to be an excellent tool for observe action potentials. There are prospects for applications that mimic human vision. In a biological system, information in the brain is transmitted through electrical and chemical impulses, generating an action potential. In this experiment, as depicted in Figure 2, a PWM (Pulse Width Modulation) signal is responsible for emulating the behavior of the action potential. However, as observed in the curves, memristor under illumination with LEDs of different wavelengths induces modifications in the signal. The measurement was conducted on an equivalent resistance to serve as a reference for comparison.

Figure 1. Hysteresis shift influenced by the incidence of light

### References

[1] A. Sharma et al., International Nano Letters, 2020.

Figure 2. Action potential emulation with different illumination conditions

### Self-rectifying Two-terminal Vertical Floating Memristor

Mihyang Park<sup>1</sup> and Woojong Yu<sup>1</sup>

<sup>1</sup>[Department of Electrical and Computer Engineering, Sungkyunkwan University, Republic of Korea] \*E-mail: micco21@skku.edu

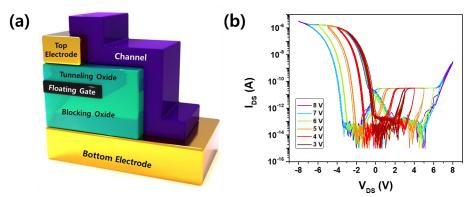

High-performance artificial synaptic devices are essential for developing energy-efficient neuromorphic computing systems. Consequently, various types of memristive devices are being studied. Among these devices, RAM has a vertical two-terminal structure with two electrodes, which allows for a high memory integration<sup>[1],[2]</sup>. In contrast, floating gate memristors have only been researched in a horizontal two-terminal<sup>[3]</sup> or three-terminal structure<sup>[4],[5]</sup>, which leads to low memory integration. To overcome this issue, we propose a two-terminal vertical tunneling random-access memory (VTRAM). VTRAM has a vertical structure of ZnO/Au/Al<sub>2</sub>O<sub>3</sub>/Pt/Al<sub>2</sub>O<sub>3</sub>/Au, where ZnO, Al<sub>2</sub>O<sub>3</sub> and Pt serves as the channel, insulator, and floating gate respectively. VTRAM exhibits both self-rectifying and non-volatile memory effects simultaneously. This self-rectifying effect can suppress sneak currents when crossbar array is fabricated, reducing the need for additional selectors and increasing integration density. Our VTRAM shows rectification ratio of 10<sup>5</sup> for the self-rectifying behavior and on/off ratio of 10<sup>7</sup> for the memory behavior. Furthermore, VTRAM has long retention time over 10,000 s and stable switching cycle of 10,000 times.

Figure 1. (a) Structure of VTRAM (b) I-V curve of VTRAM measured by varying the voltage sweep ranges from 3 to 8 V

- [1] Zhao, X. et al., Advanced materials, 30(14), 1705193, 2018

- [2] Sun, L., Zhang, Y., Han, G. et al. Nature Communications, 10, 3161, 2019

- [3] Vu, Q. A. et al., *Nature Communications*, 7(1), 12725, 2016

- [4] Wu, L., Wang, A., Shi, J. et al., Nature Nanotechnology, 16(8), 882-887 (2021).

- [5] Liu, L., Liu, C., Jiang, L. et al. Nature Nanotechnology, 16(8), 874-881 (2021)

# Reconfigurable Non-volatile Floating Gate Memory based on van der Waals Heterostructure for Multi-functional Devices

Minh Chien Nguyen<sup>1</sup>, Ngoc Thanh Duong<sup>2</sup>, Vu Khac Dat<sup>2</sup>, Van Dam Do<sup>1</sup>, Van Tu Vu<sup>1</sup>, and Woo Jong Yu<sup>1,\*</sup>

<sup>1</sup>Department of Electrical and Computer Engineering, Sungkyunkwan University, Suwon 16419, Republic of Korea

<sup>2</sup>Department of Energy Science, Sungkyunkwan University, Suwon 16419, Republic of Korea

\*E-mail: chiennguyen@g.skku.edu, micco21@skku.edu

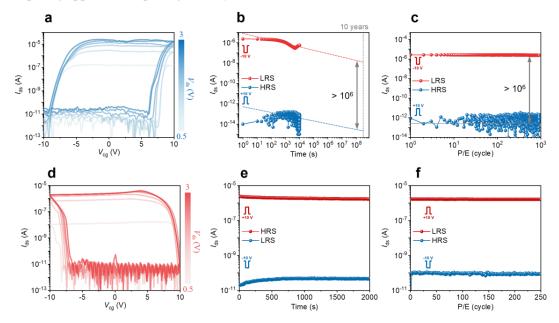

Bio-inspired computing, which mimics the functionality of biological neural networks, offers a promising solution to the von Neumann bottleneck.<sup>[1,2]</sup> This bottleneck arises from the necessity of transferring data between memory and processing units, leading to redundant information processing and increased power consumption.<sup>[3]</sup> Floating-gate memory devices based on two-dimensional materials exhibit long-term synaptic plasticity with both electrical and optical stimuli.<sup>[4-6]</sup> However, they face challenges in achieving reconfigurability for multifunctional applications. In this study, we introduce a reconfigurable non-volatile floating gate memory based on a graphene floating-gate, h-BN insulating layer, and tungsten diselenide semiconductor (Gr/h-BN/WSe<sub>2</sub>) heterostructure. By modulating the asymmetric source and drain contacts, we achieve both n-type and p-type non-volatile memory behaviors (Figure 1). The coupling of electrical and optical stimuli in the synapse enables hetero-synaptic plasticity, with relaxation timescales tunable via light intensity or control-gate voltage. This novel structure of asymmetric floating gate memory devices holds significant potential for integration into sensormemory and computing applications, paving the way for advancements in modern electronics.

Figure 1. Reconfigurable floating gate memory based on Gr/h-BN/WSe<sub>2</sub> heterostructure. (a-c) Transfer characteristics showing the n-type memory window, retention, and endurance of the n-type floating gate memory, respectively. (d-f) Transfer characteristics showing the p-type memory window, retention, and endurance of the p-type floating gate memory.

- [1] Abbott, L. F. & Regehr, W. G. Nature 431, 796-803 (2004).

- [2] Ho, V. M., Lee, J. A. & Martin, K. C. Science 334, 623-628 (2011).

- [3] van de Burgt, Y. et al., Nat. Mater. 16, 414-418 (2017).

- [4] Vu, Q. A. et al, Nat. Commun. 7, 12725 (2016).

- [5] Won, U.Y., et al. Nat Commun 14, 3070 (2023).

- [6] Tran, M. D., et al. Advanced Materials, 31(7), 1807075 (2019).

### Development and Resistive Switching Properties of Amorphous GaO<sub>x</sub> Four-Terminal Crossbar Memristor

N. Yamashita<sup>1</sup>, Y. Hayashi<sup>1</sup>, T. Tohei<sup>1</sup> and A. Sakai<sup>1\*</sup>

<sup>1</sup>Graduate School of Engineering Science, Osaka University, 1-3 Machikaneyama-cho, Toyonaka-shi, Osaka, Japan

\*Corresponding author Email: sakai@ee.es.osaka-u.ac.jp

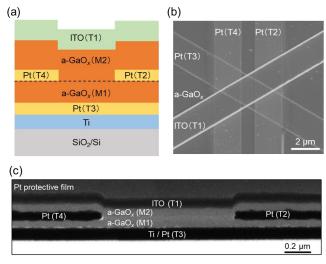

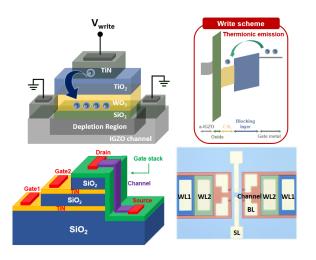

**Background**: An amorphous  $GaO_x$  (a- $GaO_x$ ) memristor is promising in terms of exhibiting non-filamentary type resistive switching properties as well as the feasibility of high-temperature operation.<sup>1</sup> Recently, we have been developing four-terminal planar memristor devices using a- $GaO_x$  to mimic higher-order synaptic (or hetero-synaptic) characteristics that are difficult to obtain with conventional two-terminal devices.<sup>2</sup> However, the planar devices are limited to achieve high-density integration. In this study, we report the fabrication and characterization of prototypic four-terminal crossbar memristor devices using a- $GaO_x$ . The present device provides a fundamental unit of integrated four-terminal crossbar array memristor architectures.

**Experimental Method**: Four-terminal crossbar memristor was fabricated on SiO<sub>2</sub>/Si substrates (Fig. 1(a)). We used electron beam lithography and lift-off processes to pattern each layer of the device. The Pt/Ti layer for the bottom electrode (T3) and Pt for the gate electrodes (T2, T4) were deposited using electron beam evaporation. The memristive a-GaO<sub>x</sub> layers (M1, M2) and the ITO layer for the top electrode (T1) were deposited using a pulsed laser deposition under a low-pressure argon (2.0 Pa) and oxygen (3.5 Pa) atmosphere, respectively. Planview scanning electron microscopy (SEM) and cross-sectional transmission electron microscopy (TEM) images of the crosspoint in our fabricated four-terminal device are shown in Figs. 1(b) and 1(c), respectively.

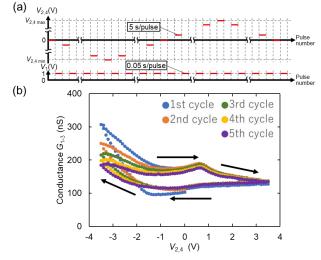

**Experimental Results**: Figure 2 (a) shows the voltage application protocol for measuring resistive change characteristics. Write voltages  $V_{2,4}$  were simultaneously applied to T2 and T4 for 5 s while T1 and T3 were grounded. Then  $G_{1-3}$ , the conductance value between T1 and T3, was measured by applying a read voltage  $V_1$  of 1 V to T1 for 50 ms while T3 was grounded. This cycle was repeated by changing  $V_{2,4}$  in the range between the minimum voltage value  $V_{2,4 \min}$  and the maximum voltage value  $V_{2,4 \max}$  in 0.1 V steps. The measurement results for  $V_{2,4 \min}$ =-3.5 V and  $V_{2,4 \max}$ =3.5 V are shown in Fig. 2 (b). Initially, as  $V_{2,4}$  decreased,  $G_{1-3}$  increased to reach a high conductance state (HCS). Then, with increasing  $V_{2,4}$ ,  $G_{1-3}$  gradually decreased showing a plateau around 0 V, then further decreased and reached a low conductance state (LCS) at  $V_{2,4 \max}$ . The LCS was maintained when  $V_{2,4}$  was decreased again, forming a loop where  $G_{1-3}$  exhibits HCS and LCS depending on  $V_{2,4}$ . We also observe gradual decrease of  $G_{1-3}$  in HCS at  $V_{2,4 \min}$  when the  $V_{2,4}$  voltage sweep is repeated, which was found to be related to the retention property of this device. The present results demonstrate the successful resistance switching operation of our four-terminal crossbar a-GaO<sub>x</sub> memristor devices and the feasibility of integrated multi-terminal memristor array architectures.

Acknowledgments: This work was partially supported by a KAKENHI Grant-in-Aid (JP20H00248, JP23H01687, JP24K00926) from the Japan Society for the Promotion of Science (JSPS).

References: [1] K. Sato et al., Sci. Rep. 13, 1261, 2023. [2] T. Ikeuchi et al., Appl. Phys. Express 16, 015509, 2023.

**Figure 1.** (a) Cross-sectional schematic and (b) plan-view SEM images of the fabricated device. (c) Cross-sectional TEM image of the four-terminal crosspoint of the fabricated device.

**Figure 2.** (a) Voltage application protocol of  $V_{2,4}$  and  $V_1$ . (b) Variation of  $G_{1-3}$  after respective steps of  $V_{2,4}$  application. Blue, orange, green, yellow and purple curves show the first, second, third, fourth and fifth cycles of the  $V_{2,4}$  applications, respectively.

### **Reconfigurable Devices for Enhanced Reservoir Computing**

Nestor Ghenzi<sup>1,2</sup>, Tae Won Park<sup>1</sup>, Kyung Seok Woo<sup>1</sup>, Hyungjun Park<sup>1</sup>, Yonghee Lee<sup>1</sup> and Cheol Seong Hwang<sup>\*1</sup> <sup>1</sup>[Department of Materials Science and Engineering and Inter-university Semiconductor Research Center, College of Engineering, Seoul National University, Seoul, 08826, Republic of Korea]

<sup>2</sup>[Universidad de Avellaneda and Consejo Nacional de Investigaciones Científicas y Técnicas, Avellaneda, Buenos Aires 1872,

Argentina]

\*E-mail: [cheolsh@snu.ac.kr]

Reservoir Computing (RC) is a machine-learning algorithm for processing time-series signals generated by complex dynamical systems, emulating the human brain's highly nonlinear and recursively interconnected architectures. It is a type of recurrent neural network that employs a "reservoir" as a dynamic feature extractor to process sequential or time series data. The reservoir layer is a vital component of the RC system, extracting features from the temporal input data. The main advantage of the RC is the minimal training data sets and an easy training process through a compact structure. Nonetheless, the conventional RC system has been primarily software-based, assuming its operation in the CMOS circuits. Such RC systems undermine their crucial merits due to extensive data use, which is the critical hurdle of the current von Neumann computing system<sup>1</sup>.

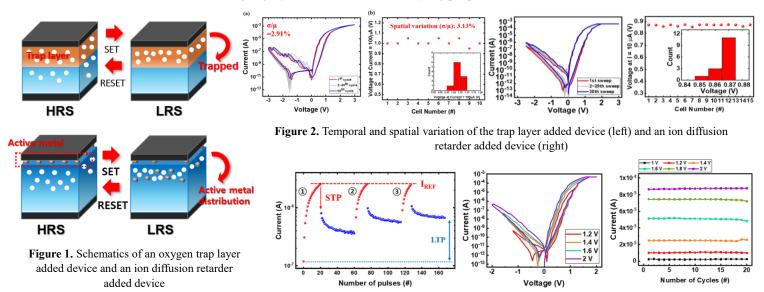

This work investigates the potential of reconfigurable devices to enhance RC performance by generating diverse nonlinear dynamics within the reservoir (Figure 1a). Three distinct devices are adopted using their unique physical mechanisms that exhibit volatile nonlinear behaviors, demonstrating that integrating multiple reservoir units with varying dynamics significantly enhances overall RC performance. The first device is a  $Pt/Ta_2O_5/HfO_2/TiN$  memristor, which leverages the electronic trapping properties of  $HfO_2$  combined with either a self-rectifying or a resistive  $Ta_2O_5$  layer (Figure 1b). The different microscopic configurations lead to distinct relaxation behaviors, thereby diversifying the reservoir dynamics. The second device is a  $CuTe/HfO_2/Pt$  memristor, which employs a CuTe filament within a trapping device (Figure 1c). Its volatile behavior can be selectively turned on or off, altering its dynamic response based on the number of active devices within the reservoir. The last device is a two IGZO transistor structure (2T0C) working as a gain cell. By controlling the  $V_{GATE}$  of the write transistor, the nonlinearity in the current relaxation can be monotonically tuned, providing fine control over the reservoir dynamics (Figure 1d). Integrating reconfigurable units with diverse behaviors within the reservoir overcomes the limitations of previous hardware implementations and highlights a promising pathway toward more robust and efficient RC systems.

**Figure 1.** (a) Heterogeneous reservoir computing structure where the reservoir units present different dynamic response. (b) Reservoir composed of self-rectifying and leaky  $Pt/Ta_2O_5/HfO_2/TiN$  memristor, resulting in a 5% performance increase. (c) CuTe/HfO\_2/Pt memristor based- reservoir presents a strong separability for 4-bit pulse pattern due to the different Cu filament morphology. (d) 2T0C gain cell device structure allows the fine control of the relaxation dynamics by means of  $V_{GATE}$ .

#### References

[1] Nestor Ghenzi et al., Nanoscale Horizons, 9, 427-437, 2024.

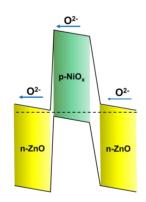

### Self-selective Crossbar Synapse Array with n-ZnO/p-NiO<sub>x</sub>/n-ZnO Structure for Neuromorphic Computing

Peter Hayoung Chung<sup>1</sup> and Tae-Sik Yoon<sup>1</sup>

<sup>1</sup>[Graduate School of Semiconductor Materials and Devices Engineering, Ulsan National Institute of Science and Technology,

Republic of Korea]

\*E-mail: [tsyoon@unist.ac.kr]

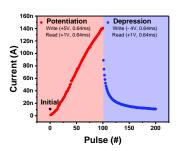

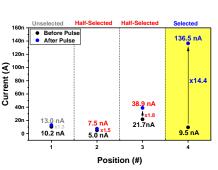

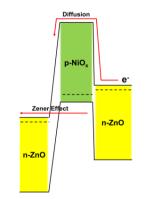

Artificial synapse devices are essential elements for highly energy-efficient neuromorphic computing, which can overcome the current bottle neck issue of the von Neuman computing system<sup>1,2</sup>. They are implemented as crossbar array architecture, where highly selective synaptic weight update for training and sneak leakage-free inference operations are required. In this study, self-selective bipolar artificial synapse device was proposed with n-ZnO/p-NiO<sub>x</sub>/n-ZnO heterojunction and its analog synapse operation with high selectivity was demonstrated in  $32 \times 32$  crossbar array architecture without the aid of selector devices (Figure 1 and Figure 2). The built-in potential barrier at p-NiO<sub>x</sub>/n-ZnO junction and the additional current flow due to Zener tunneling effect provided nonlinear current-voltage characteristics at both voltage polarities for self-selecting function for synaptic potentiation and depression operations (Figure 3). Voltage-driven redistribution of oxygen ions inside n-p-n oxide structure, evidenced by x-ray photoelectron spectroscopy, modulated the distribution of oxygen vacancies in the layers and consequent conductance in an analog manner for synaptic weight update operation (Figure 4). It demonstrated that the proposed n-p-n oxide device is a promising artificial synapse device implementing self-selectivity and analog synaptic weight update in a crossbar array architecture for neuromorphic computing.

**Figure 1.** Synaptic analog conductance modulation behavior

**Figure 2.** Highly selective conductance modulation in 32×32 crossbar array device

Figure 3. Nonlinear currentvoltage characteristics due to built-in potential barrier and Zenner tunneling effect

Figure 4. Change of energy band by voltage-driven redistribution of oxygen ions resulting analog conductance modulation

#### References

[1] N.K. Upadhyay et al., Advanced Materials Technology, 4(4), 1800589, 2019

[2] X. Duan et al., Advanced Materials, 36(14), 2310704, 2024

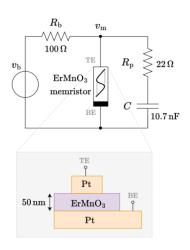

### An ErMnO<sub>3</sub> memristive spiking neuristor

Richard Schroedter<sup>1</sup>, Ahmet Samil Demirkol<sup>1</sup>, Rong Wu<sup>2,3</sup>, Catherine Dubourdieu<sup>2,3</sup>, and Ronald Tetzlaff<sup>1</sup>

<sup>1</sup>Chair of Fundamentals of Electrical Engineering, Technische Universität Dresden, GERMANY

<sup>2</sup>Helmholtz Zentrum Berlin für Materialien und Energie, GERMANY

<sup>3</sup>Freie Universität Berlin, Physical and Theoretical Chemistry, GERMANY

\*E-mail: richard.schroedter@tu-dresden.de

We present a novel ErMnO<sub>3</sub> memristive device exhibiting a negative differential resistance (NDR) region. By biasing this device in the NDR region and including a RC circuit, we have created a spiking neuristor capable of emulating the leaky-integrate-and-fire behavior of biological neurons, see Figures 1-3. The neuristor leverages the local activity phenomenon in the volatile memristive threshold switching device, enabling it to mimic the spike dynamics of natural neurons. Despite advances that have been achieved by utilizing NbO<sub>2</sub> and VO<sub>2</sub>-based NDR devices, controlling their reliability and the spiking frequency range remains challenging due to their temperature-driven mechanisms. With a focus on this aspect, we developed a compact model, which describes accurately the experimentally measured behavior at room and elevated temperatures, and predicts the internal temperature during the neuristor operation. The model expands our previous research [1] and treats the internal temperature as the memristor state variable while assuming Poole-Frenkel emission [2] as the primary mechanism combined with an internal bipolar diode behavior. Following the strong agreement between DC experimental data and the proposed model, see Figure 2, we extracted analytically the element values of the small-signal equivalent circuit parameters, including the equivalent inductance in the locally active region.

In order to determine the most reliable operation across a wide frequency range, we explored different biasing schemes while carefully tuning the element values of the circuit depicted in Figure 1. We observed a consistent and reliable spike response with minimal jitter and noise throughout the experiments. The proposed model can accurately reproduce the same waveform response observed in the measurements, as shown in Figure 3. The spike interval frequency can be varied from 100 kHz to 300 kHz by adjusting the input source voltage or biasing regime. By utilizing our neuristor model, we designed a trade-off between resistive damping and limiting the internal temperature, ensuring safe operation and preventing unintentional non-volatile behavior by not exceeding the annealing temperature of the device. Finally, we simulated our model in SPICE and demonstrated a spike propagation along neuristor cells. This research aims to pave the way for low-power hardware implementations of spiking neural networks, capitalizing on their sparse and event-based operation paradigm to effectively conserve energy.

Figure 1. Neuristor circuit to bias the ErMnO<sub>3</sub> device in the NDR region. The device is connected via a probe station with the external biasing circuit.

$v_{\rm m}~({\rm V})$ Figure 2. Static and dynamic phase diagrams: memristor current (upper) and internal temperature state (lower) versus memristor voltage. Experimental DC data (green dots)

overlap with DC model (black dashed line).

Figure 3. Time responses for memristor voltage (upper) and internal temperature state (lower). Experimental data (red dots) and dynamic model (black line) show same waveform at a spike frequency of 130 kHz.

[1] A.S. Demirkol et al, *IEEE International Symposium on Circuits and Systems (ISCAS). pp. 1-5*, 2021 [2] Z. Wang et al, *Applied Physics Letters 112, 193503*, 2018

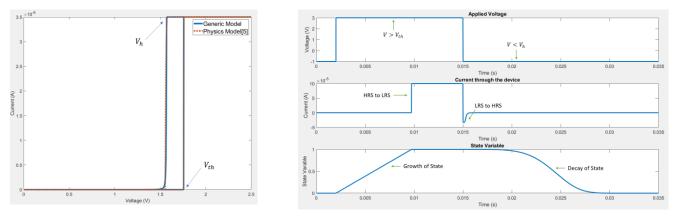

### **V-VTEAM: A Compact Behavioral Model for Volatile Memristors**

Tanay Patni<sup>1</sup>, Rishona Daniels<sup>1\*</sup> and Shahar Kvatinsky<sup>1</sup>

<sup>1</sup>[Viterbi Faculty of Electrical and Computer Engineering, Technion – Israel Institute of Technology, Israel]

\*E-mail: [rishonad@campus.technion.ac.il]

Volatile memristors have recently gained popularity as promising devices for neuromorphic circuits, capable of mimicking the leaky function of neurons and offering advantages over capacitor-based circuits in terms of power dissipation and area. Additionally, volatile memristors are useful as selector devices and for hardware security circuits such as physical unclonable functions. To facilitate the design and simulation of circuits, a compact behavioral model is essential. This paper proposes V-VTEAM, a compact, simple, general, and flexible behavioral model for volatile memristors, inspired by the VTEAM nonvolatile memristor model and developed in MATLAB. The validity of the model is demonstrated by fitting it to an ion drift/diffusion-based Ag/SiOx/C/W volatile memristor, achieving a relative root mean error square of 4.5%.

**Figure 1.** Proposed Generic Model fitted to an ion drift/diffusion-based Ag/SiOx/C/W volatile memristor model [5].

Figure 2. The applied voltage, current, and state variable of the proposed volatile memristor model

- [1] Y. Xiao et al., Sci. Technol. Adv. Mater., 24(1), Taylor and Francis Ltd., 2023.

- [2] F.-X. Liang et al., Adv. Intell. Syst., 3(8), 2021.

- [3] S. M. Kang et al., IEEE Trans. Circuits Syst. I: Regul. Pap., 68(12), 4837, 2021.

- [4] D. Kim et al., Appl. Phys. Lett., 121(1), 2022.

- [5] W. Wang et al., IEEE Trans. Electron Devices, 66(9), 3802, 2019.

- [6] P. Y. Chen et al., IEEE Trans. Electron Devices, Vol. 62, No. 12, pp. 4022-4028, December 2015.

- [7] Z. Jiang et al., SISPAD 2014, Yokohama, Japan, 41, 2014.

- [8] S. Kvatinsky et al., IEEE Trans. Circuits Syst. II Express Briefs, 62(8), 786, 2015.

- [9] T. Chang et al., ACS Nano, 5(9),7669, 2011.

- [10] J. Snyman, 97, Springer, 2005.

- [11] S. P. Brooks, The Statistician, 44(2), 241, 1995.

- [12] https://github.com/tanaypatni03/Generic-Volatile-Memristor-Model

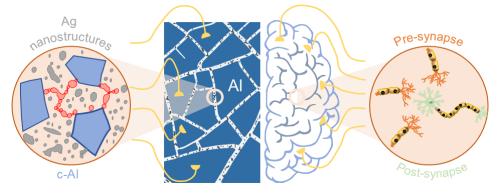

# Emergence of *In Materia* Intelligence in Energy-efficient Neuromorphic Devices realized using Self-forming Hierarchical Structures

Rohit Attri<sup>1</sup>, C. N. R. Rao<sup>1,2</sup> and G. U. Kulkarni<sup>2\*</sup>

<sup>1</sup>[New Chemistry Unit and School of Advanced Materials (SAMat), Jawaharlal Nehru Centre for Advanced Scientific Research, Bengaluru 560064, INDIA]

<sup>2</sup>[Chemistry and Physics of Materials Unit and School of Advanced Materials (SAMat), Jawaharlal Nehru Centre for Advanced

Scientific Research, Bengaluru 560064, INDIA]

\*E-mail: [rohit@jncasr.ac.in]